| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- 교차 엔트로피

- 자료구조 알고리즘

- 인공지능

- 뇌를 자극하는 알고리즘

- 단층 퍼셉트론

- 파이썬 딥러닝

- 딥러닝 교차 엔트로피

- 컴퓨터구조

- lost function

- 확률분포

- 오퍼랜드

- 엔트로피

- 자료구조

- 딥러닝 교차엔트로피

- 퍼셉트론

- DBMS

- 파이썬 날코딩으로 알고 짜는 딥러닝

- 딥러닝

- 연결 자료구조

- 회귀분석

- DB

- 순차 자료구조

- 리스트

- 단층퍼셉트론

- 자연어처리

- 노드

- 편미분

- 선형 리스트

- 파라미터

- 신경망

- Today

- Total

YZ ZONE

[ 컴퓨터구조 ] 5.6 DDR SDRAM 본문

DDR SDRAM

▣ DDR SDRAM

▪ 기억장치의 액세스 속도는 CPU에 비하여 현저히 낮음

▪동영상 처리, 음성/영상 압축과 같은 대규모 데이터 처리 응용 증가 ➔주기억장치 병목 현상 심화

▪ 기억장치 액세스 및 데이터 전송률 향상 기술 개발

➢SDRAM

➢DDR SDRAM

SDRAM

▣ 동기식 DRAM(Synchronous DRAM: SDRAM)

▪ 액세스 동작들이 시스템 클록에 맞추어(동기화 되어) 수행되는 DRAM

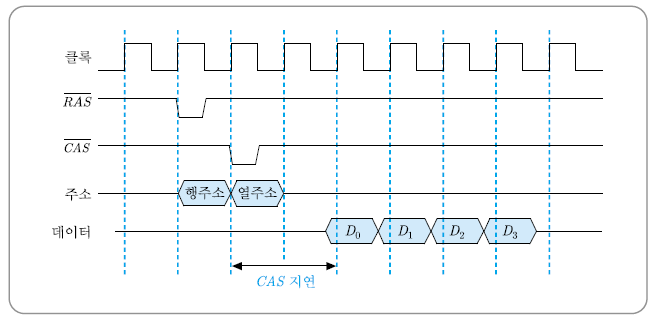

[예] 읽기 동작

1. CPU는 한 클록 주기 동안에 시스템 버스를 통하여 주소와 읽기 신호 를 기억장치로 보낸 후, 그 결과를 기다리지 않고 내부적으로 다른 연 산을 수행

2. SDRAM은 주소와 읽기 신호를 받은 즉시 읽기 동작을 시작하며, 그 동작이 완료되면 시스템 버스 사용권을 획득한 후, 다음 클록 주기 동 안에 버스를 통하여 CPU로 데이터 전송

3 .CPU는 그 데이터를 받아서, 다음 연산을 수행

SDRAM의 내부 조직

▣ 다수의 뱅크(bank)들로 구성: 뱅크 별로 동시 액세스 가능

[예] 512Mbit SDRAM

▪ 4개의 16Mx8bit 뱅크들로 구성 : 4x16Mbyte = 64Mbyte

▪ 주소 비트 수 = 26, 최상위 2비트: 뱅크 선택(bank select)에 사용

▣ 행(row): 8K 개의 기억소자 배열(memory cell array)

▣ 각 배열에는 16Kbit (2KBytes) 씩 저장

▣ 칩의 입출력(데이터) 선의 수 : 8

➔ 행 주소(row addr) = 13비트, 열 주소(column addr) = 11비트

▣ 읽기 동작 시, 각 배열의 데이터(2KByte) 전체가 감지 증폭기(sense amplifier)로 이동 = ‘행 열기(opening the row)’ ➔ 그런 다음에, 열 주소에 의해 바이트(8 비트) 단위로 데이터 버스에 실림

▣ 버스트 모드(burst mode): 여러 바이트들을 연속적으로 전송하는 동작

▣ 버스트 길이(burst length): 각 버스트 동작 동안에 전송되는 데이터 바이 트들의 수

버스트 읽기 동작의 타이밍 도 (버스트 길이 = 4)

▣ CAS 지연(latency): CAS 신호와 열 주소가 들어온 순간부터 데이터 가 인출되어 버스에 실릴 때까지의 시간(주소 해독 및 액세스 시간)

▣ 버스트 모드의 효과: 버스 사용권을 한 번 획득한 후, 여러 클록 동 안 연속 전송 가능 (위 그림의 경우: 버스트 길이 = 4)

▣ 기억장치 모듈(memory module) 구성의 필요성

▪ SDRAM의 데이터 입출력 폭 = 8비트

▪ 단어 단위의 데이터 액세스를 위하여 여러 개의 SDRAM 칩들을 병렬로 접속하여 기억장치 모듈을 구성

[예] 64-비트 컴퓨터시스템을 위한 기억장치 모듈

▪ 8개의 64Mx8bit SDRAM 칩들을 병렬 접속

➔ 64비트씩 읽기/쓰기 가능한 512MByte 기억장치 모듈

▣ 기억장치 모듈 당 SDRAM 칩 한 개를 추가➔8-비트 길이의 ECC(error-correction code)를 같이 저장

512MB 기억장치 모듈의 모습

그림 5-33. 512MByte SDRAM 기억장치 모듈

(중간 소켓에 ECC 칩 추가 가능)

DDR SDRAM

▣ SDRAM 기억장치 모듈의 대역폭(bandwidth)을 향상시키기 위한 기술

▪ 대역폭: 단위 시간 당 전송되는 데이터 량, 단위: [bytes/sec]

▣ DDR(double data rate) SDRAM : 버스 클록 당 두 번의 데이 터 전송 (클록 펄스의 상승-에지 및 하강-에지에서 각각 전송)

[비교] SDRAM: SDR(single data rate) SDRAM에 해당

▣ DDR2 SDRAM : DDR SDRAM과 같으며, 버스 클록 주파수를 두 배로 높여 대역폭 향상

▣ 읽기 시간 비교 (예: 버스트 길이 = 8)

▪SDR @ 133 MHz [PC133]

➢버스 클록 = 133MHz

➢매 클록 주기(7.5ns)마다 64비트씩 전송

➢8번의 데이터 전송에 걸리는 시간 = CAS 지연(15ns) + (7.5nsx8) = 75ns

▪DDR @ 133 MHz [DDR-266]

➢상승 및 하강 에지에서 64비트씩 전송

➢8번의 데이터 전송에 걸리는 시간 = CAS 지연(15ns) + {(7.5ns/2)x8} = 45ns

▪DDR-2 @ 266 MHz [DDR-533]

➢버스 클록 = 266 MHz (주기 = 3.75ns)

➢상승 및 하강 에지마다 64비트씩 전송

➢8번의 데이터 전송에 걸리는 시간 = CAS 지연(15ns) + {(3.75ns/2)x8} = 30ns

➢데이터 전송시간(CAS 지연 제외) 비교 : 60ns (SDR)→30ns (DDR)→15ns (DDR-2)

▣ DDR 기술의 기본 원리

▪ 버스 클록의 상승 에지와 하강 에지에서 각각 데이터 전송

▪ 기억장치 제어기(memory controller) 및 버스 인터페이스 회로의 개선을 통하여 버스 클록 주파수 향상

★ DDR3 및 DDR4도 같은 원리를 적용하여 설계

▣ 기억장치 대역폭(memory bandwidth)

▪ 단위 시간 당 데이터 전송량

▪ 버스 폭(bus width) x 클록 주파수

[예] 데이터 버스 = 64비트, 버스 클록 주파수 = 100MHz

➔ 대역폭 : (100MHz x 64) / 8비트 = 800[Mbytes/sec]

SDR @133MHz : (133MHz x 64) / 8 = 1064[Mbytes/sec]

DDR @133MHz : (133MHz x 2 x 64) / 8 = 2128[Mbytes/sec]

DDR2 @266MHz : (266MHz x 2 x 64) / 8 =4256[Mbytes/sec]

▣ CAS 지연

▪ DDR (그림 5-34(b): SDRAM 칩의 CAS 지연 = 15ns 일 때, 클록 주기가 7.5ns이므로, CAS 지연 = 2주기

▪ DDR2 (그림 5-34(c)): f = 266MHz (클록 주기 = 3.75ns) → CAS 지연 = 4주기 (15ns / 3.75ns = 4주기)

▪ DDR3 및 DDR4에 사용되는 SDRAM 칩들의 CAS 지연 = 10ns

➢DDR3-1600 @800MHz : CAS 지연 = 8주기

➢DDR4-3600 @1800MHz : CAS 지연 = 16주기

'IT > 컴퓨터구조' 카테고리의 다른 글

| [ 컴퓨터구조 ]5.7 차세대 비휘발성 기억장치 (1) | 2023.02.15 |

|---|---|

| [ 컴퓨터구조 ] 5.6.2 DDR SDRAM (0) | 2023.02.15 |

| [ 컴퓨터구조 ] 5.5.3 캐시 기억장치 (계속) (0) | 2023.02.08 |

| [ 컴퓨터구조 ] 5.5.2 캐시 기억장치 (계속) (0) | 2023.02.08 |

| [ 컴퓨터구조 ] 5.5 캐시 기억장치 (0) | 2023.02.08 |