| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- 단층 퍼셉트론

- 확률분포

- 퍼셉트론

- 오퍼랜드

- 신경망

- 인공지능

- 파라미터

- 노드

- 딥러닝 교차엔트로피

- 순차 자료구조

- 자료구조 알고리즘

- 선형 리스트

- 딥러닝 교차 엔트로피

- DB

- 교차 엔트로피

- 파이썬 딥러닝

- 자료구조

- 편미분

- 엔트로피

- DBMS

- 파이썬 날코딩으로 알고 짜는 딥러닝

- 단층퍼셉트론

- 리스트

- 연결 자료구조

- 컴퓨터구조

- 뇌를 자극하는 알고리즘

- lost function

- 회귀분석

- 딥러닝

- 자연어처리

- Today

- Total

YZ ZONE

[ 컴퓨터구조 ] 5.5.3 캐시 기억장치 (계속) 본문

큰 용량의 세트-연관 사상 캐시 조직의 예

▣ 큰 용량의 세트-연관 사상 캐시 조직의 예

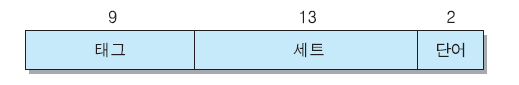

▪ 주기억장치의 용량은 16M (224)바이트이다. 따라서 주기억장치의 주소는 24비트이고, 바이트 단위로 주소가 지정된다.

▪ 주기억장치는 4-바이트 크기의 블록들 4M (222)개로 구성되어 있다. 그리 고 단어의 길이는 한 바이트이다.

▪ 캐시의 용량은 64K (216)바이트이다.

▪ 주기억장치의 블록 크기가 4바이트이므로, 캐시 라인의 크기도 4바이트가 되며, 결과적으로 라인 수 m = 16K (214 )개가 된다.

▪ 2-way 세트-연관 사상 조직으로 가정한다. 따라서 세트의 수 v = 8K (213 ) 개 이다.

▣ 기억장치 주소 형식

▣ 각 세트가 공유하는 주기억장치 블록들

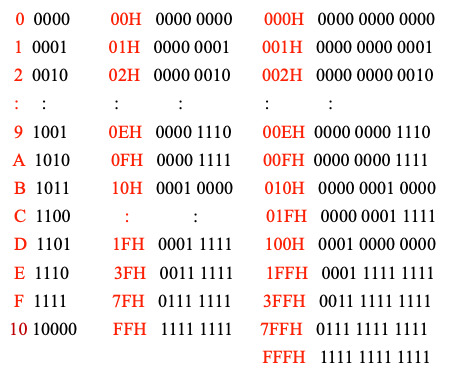

64KByte 크기의 2-way 세트-연관 캐시의 예

[참고] 16진수(Hexadecimal number)

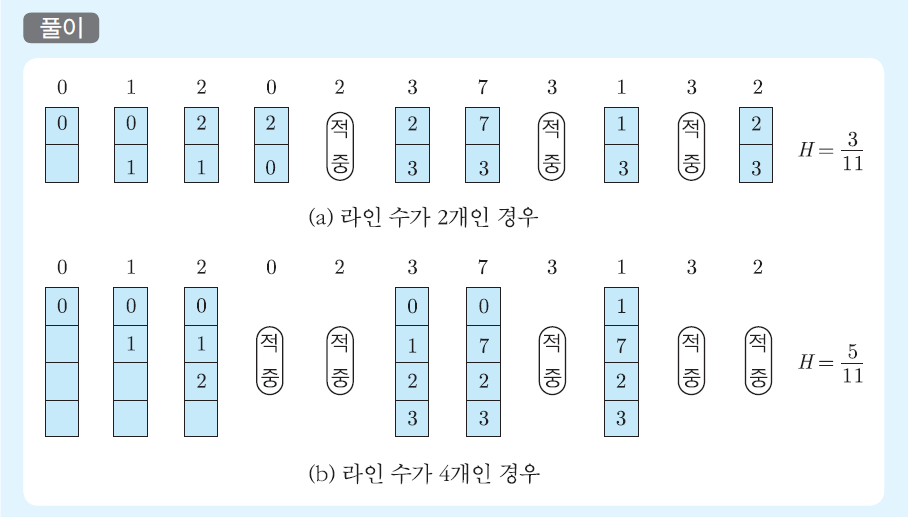

교체 알고리즘

▣ 세트-연관 사상에서 주기억장치로부터 새로운 블록이 캐시로 적 재될 때, 만약 세트 내 모든 라인들이 다른 블록들로 채워져 있다면, 그들 중의 하나를 선택하여 새로운 블록으로 교체

▣ 교체 알고리즘 : 캐시 적중률을 극대화할 수 있도록 교체할 블록을 선택하기 위한 알고리즘

▪ 최소 최근 사용(Least Recently Used: LRU) 알고리즘 : 사용되지 않은 채로 가장 오래 있었던 블록을 교체하는 방식

▪ FIFO(First-In-First-Out: FIFO) 알고리즘 : 캐시에 적재된 지 가장 오래된 블 록을 교체하는 방식

▪ 최소 사용 빈도(Least Frequently Used: LFU) 알고리즘 : 참조되었던 횟수 가 가장 적은 블록을 교체하는 방식

▪ 임의(random) 알고리즘 : 임의로 선택해서 교체

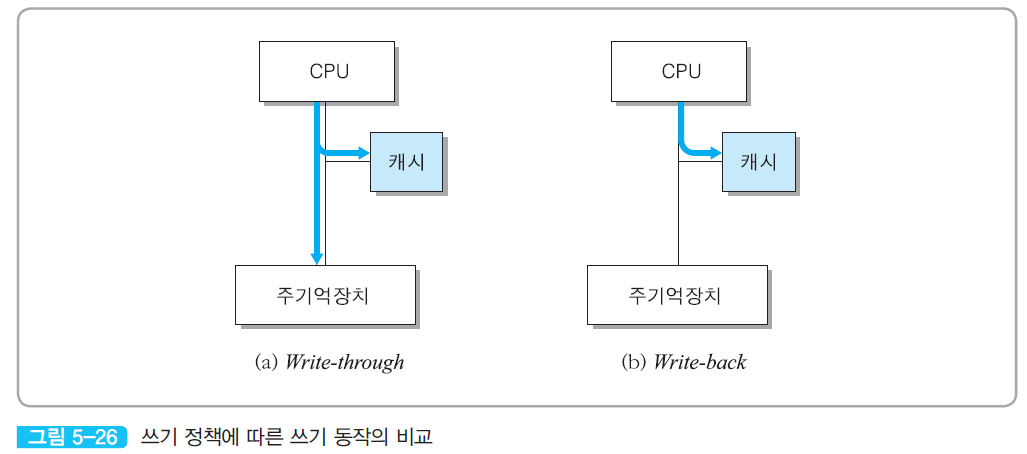

쓰기 정책 (write policy)

▣ 캐시의 블록이 변경되었을 때, 그 내용을 주기억장치에 갱신 하는 시기와 방법의 결정

▣ 종류

1. Write-through : 모든 쓰기 동작들이 캐시로 뿐만 아니라 주기억장 치로도 동시에 수행되는 방식

[장점] 캐시에 적재된 블록의 내용과 주기억장치에 있는 그 블록의 내용이 항상 같다

[단점] 모든 쓰기 동작이 주기억장치 쓰기를 포함하므로, 쓰기 시간이 길어진다

2. Write-back : 캐시에서 데이터가 변경되어도 주기억장치에는 갱신 되지 않는 방식

[장점] 기억장치에 대한 쓰기 동작의 횟수가 최소화되고, 쓰기 시간 이 짧아진다

[단점] 캐시의 내용과 주기억장치의 해당 내용이 서로 다르다(데이터 불 일치 현상)

→캐시의 데이터가 수정된 적이 있는 경우에는, 블록을 교체할 때 주 기억장치에 갱신하는 동작이 선행되어야 하며, 그를 위해 각 캐시 라 인이 상태 비트(state bit)를 가지고 있어야 한다

[참고] 다중프로세서시스템에서의 데이터 불일치 문제

▣ 다중프로세서시스템에서의 데이터 불일치 문제(data inconsistency problem) : 주기억장치에 있는 블록의 내용과 캐시 라인에 적재된 블록의 내용이 서로 달라지는 문제

▣ 캐시 일관성 프로토콜(cache coherence protocol) 필요[예] MESI 프로토콜 : [제8장 4.3절]에서 설명함.

다중 캐시(multiple cache)

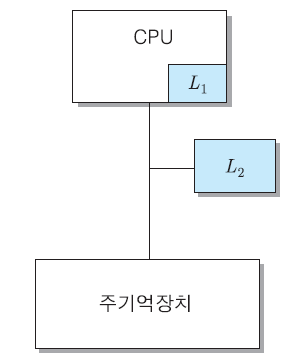

▣ 온-칩 캐시(on-chip cache) : 캐시 액세스 시간을 단축시키기 위하여 CPU 칩 내에 포함시킨 캐시 (아래 그림의 L1)

1) 계층적 캐시(hierarchical cache)

▣ 온-칩 캐시를 1차(L1) 캐시로 사용하고, 칩 외부에 더 큰 용량의 2차 (L2) 캐시를 설치하는 방식

▣ L2는 L1의 슈퍼-세트(super-set): L2 의 용량이 L1보다 크며, L1 의 모든 내용이 L2에도 존재

▣ 먼저 L1을 검사하고, 만약 원하는 정보가 L1에 없다면 L2를 검사하며, L2에도 없는 경우에는 주기억장치를 액세스

▣L1은속도가빠르지만용량이작기때문에,L2 보다적중률은더낮다

▣ 2-단계 캐시 시스템의 평균 기억장치 액세스 시간 :

Ta = H1 x TL1 + (H2 - H1) x TL2 + (1 - H2) x Tm

만약 H2가 L1에서 미스 된 액세스들에 대한 L2의 적중률이라면,

Ta= H1 xTL1 +(1-H1)H2 xTL2 +{1-H1-(1-H1)H2}xTm

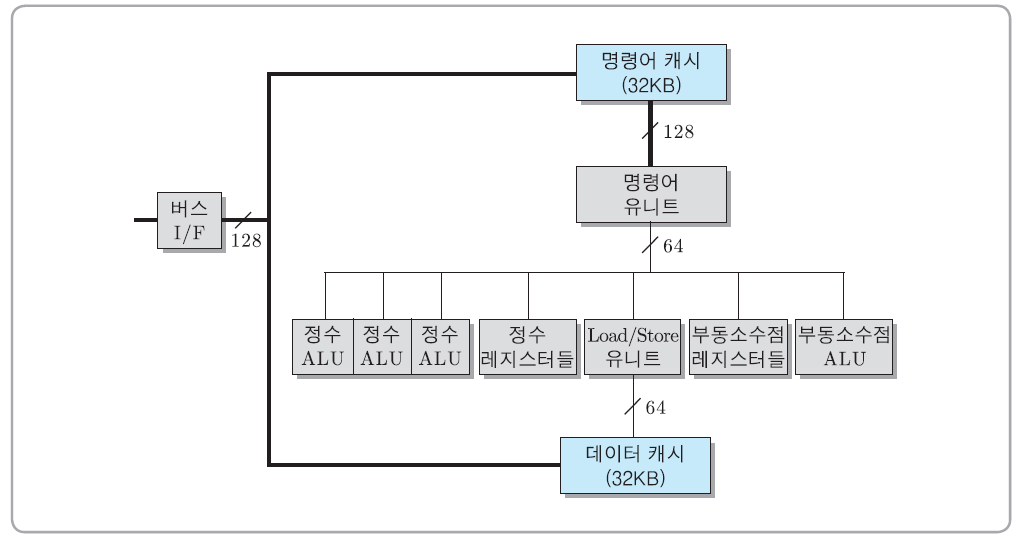

분리 캐시 (split cache)

1) 분리 캐시 (split cache)

▪ 캐시를 명령어 캐시와 데이터 캐시로 분리

▪ 명령어 인출 유니트와 실행 유니트 간의 캐시 액세스 충돌 제거

▪ 대부분의 고속 프로세서들에서 사용

계층적 분리 캐시의 사례 : 인텔 이타늄(Itanium) 프로세서

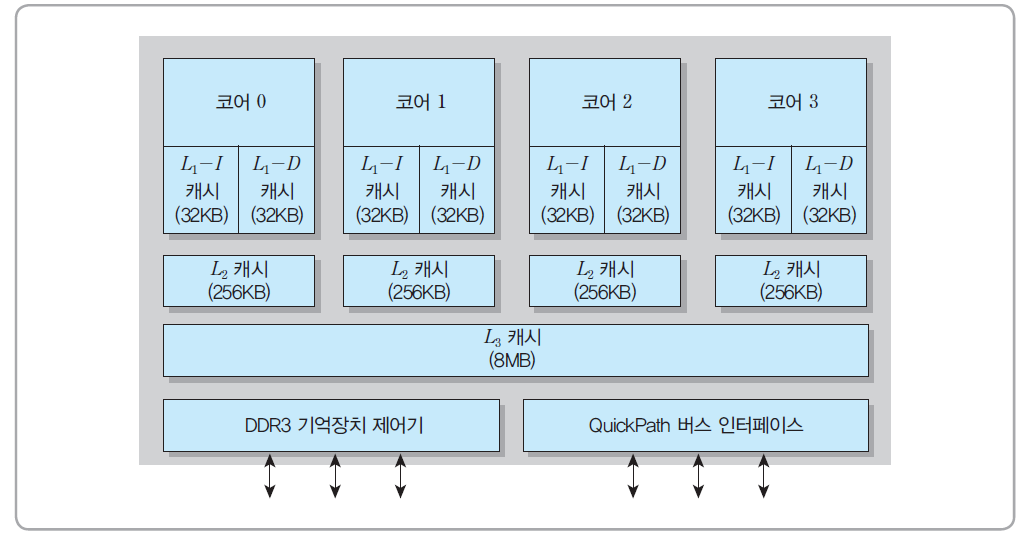

멀티-코어 프로세서의 캐시 구조

▣ [예] 인텔 i7-990X 쿼드-코어 프로세서의 3-레벨 캐시 구조

'IT > 컴퓨터구조' 카테고리의 다른 글

| [ 컴퓨터구조 ] 5.6.2 DDR SDRAM (0) | 2023.02.15 |

|---|---|

| [ 컴퓨터구조 ] 5.6 DDR SDRAM (1) | 2023.02.15 |

| [ 컴퓨터구조 ] 5.5.2 캐시 기억장치 (계속) (0) | 2023.02.08 |

| [ 컴퓨터구조 ] 5.5 캐시 기억장치 (0) | 2023.02.08 |

| [ 컴퓨터구조 ] 5.4 기억장치 모듈의 설계 (0) | 2023.02.06 |